政大勞動學報 / 第二十八期 / 民國 101 年 12 月 / 頁 45-86 Bulletin of Labour Research / No.28 / December 2012

## 晶圓廠勞動過程之探討

以時間秩序為分析角度

## 林宗德\*

<sup>\*</sup>清華大學通識教育中心暨社會學研究所助理教授, E-mail: tdlin@mx.nthu.edu.tw。

#### 摘要

當前半導體製造業的特色是研究與生產合一,以因應半導體製 程的複雜性與快速的技術變遷。半導體業的技術變遷可用所謂的「摩 爾定律」來說明:在每一到兩年內,在一積體電路晶片上可容納的 電晶體數量將會倍增。然而實驗室與工廠的合一,使得同時肩負研 究與生產功能的設備,其運轉時間的分配成為重要問題,形塑了半 導體晶圓廠中工作的時間特性。

本文分析半導體晶圓廠為求同時滿足研究與生產的需求,造就 的兩類僱員-技術員和工程師之工作的時間秩序。透過分工,技術 員不需解決生產過程中發生的問題,工作的特徵是一系列可預測次 序而持續時間短暫的事件,呈現的是「單序」之形態。相較之下, 由於半導體的製程複雜性,工程師面對不定時出現的問題,必須同 時處理各種解決所需時間不一的事件,其工作為「多序」的形態。 而由於設備運轉時間由製造部門壟斷,解決問題和製程研究所需的 實驗常無法順利取得該時間,使得工程師多序工作的形態更爲鞏固。 晶圓廠內因技術特性而構築的時間分配體制,造就了工程師長工時 的工作形態。

關鍵詞:半導體產業、半導體晶圓廠、勞動過程、時間秩序

## 壹、前言

如果不生產,連問題是什麼都不知道。現在的世界先進就是我在做次微米計畫的實驗室,實驗室就造的這麼大,那 個時候我說要不然就不要做,要做就這樣,做個不上不下的, 浪費嘛!為什麼?我要在裡面生產,工業的東西是 knowhow,光講是沒有用的,會做才重要,做了以後才知道訣竅。<sup>1</sup>

這段話道出了半導體製造業的特性。

在 1960 年代末期,美國 Intel 公司的創辦人有鑒於先前快捷 (Fairchild) 半導體公司面臨研究成果轉移至生產線上的困難,刻意 打破研究與生產的界限而不另外設置研究實驗室(Bassett, 2002: Chap 6)。如果 Intel 當時的組織安排,所欲解決的是在半導體產業發展初 期,由於研究與生產之間的巨大落差導致企業內部技術轉移的困難, 那麼目前上中下游已經完整分工的產業體系,似乎並沒有結合研究與 生產的必要。尤其半導體製程設備早已演變成由專業設備商提供的情 況下更應是如此。由於製程技術受限於設備機台的設計,目前有一大 部分的研究工作實是由設備商進行,而不似當年仍有部分半導體製造 商自行在廠內研製(Bassett, 2002: 235)。

然而就如同上引文所暗示的,研究成果與生產線上的量產技術之 間仍然有相當的距離,其中所發生的問題也僅能在等同於生產線的「實 驗室」內透過研究尋求解決。但是這一時的解決遠非一勞永逸:製程 技術微縮化的趨勢使得半導體廠持續地在重複這段過程。此趨勢可以

這是曾任職於美國 AT&T 公司貝爾實驗室(Bell Labs),後來回國主持工研院國家次 微米計畫的盧志遠博士,於 1990 年代中期任職世界先進副總經理期間受訪時的說法。 轉引自(張維安、高承恕, 1996:9)。

48 政大勞動學報/第二十八期/民國 101年12月

用所謂的「摩爾定律」(Moore's Law)來說明。

在電子資訊界為人熟知的摩爾定律,指的是在每一到兩年內,在 一積體電路晶片上可容納的電晶體(transistor)數量將會增加一倍。 摩爾定律是1965年,由快捷半導體公司的創辦人之一Gordon E. Moore (Intel 即是1968年由 Moore 與快捷半導體的另一創辦人 Robert Noyce 另創)提出,原本僅是他就當時晶片產品的技術資料所做的一個經驗 性觀察和預測。根據每年累積的新資料,透過旁人及摩爾本人數次的 詮釋、修正,與提倡(Mollick, 2006),這預測已然成為半導體界的 依循指標。成立於 1977年的美國半導體產業協會(Semiconductor Industry Association,簡稱 SIA)便根據摩爾定律來制定半導體產業 技術藍圖(Technology Roadmap),做為半導體學界與業者技術研發 時的參考。技術藍圖的目的是根據摩爾定律的預測,界定半導體製程 微縮化技術發展將會面臨的困難,並且透過組織動員投入研究資源以 謀求解決之道。因此,摩爾定律從原來基於經驗性觀察所做的預測, 變成一個「定律」,反過來主導了產業的方向(Miller and O'Leary, 2007)。

摩爾定律與半導體產業發展之間歷經數十年的相互建構與強化, 前者的預測及至目前依舊大致準確,成為科技史上著名的所謂自我實 現的預言(self-fulfilling prophecy)(Mollick, 2006: 62)。此外,甚 至有技術史家認為,它所預測的半導體技術發展軌跡數十年間少有偏 差,代表著技術決定論仍有部分解釋力(Ceruzzi, 2005)。

摩爾定律所斷言的技術進展,其基礎實際上是資本邏輯:伴隨技術進展帶來的是生產成本的持續降低,而不追隨摩爾定律預測的趨勢 則暗示著棄守市場。然而若是半導體業界皆需如同摩爾定律所指示的 那般快速地技術更新,發展生產線上量產的新技術,並且還要同時使 用既有的技術進行生產,那麼在實驗室與生產線合一的情況下,研究 與生產活動之間如何協調?再者,既有的生產也並非毫無問題。製程

的複雜性使得半導體例行的生產活動離不開發現與解決隨時發生的問題。而不論是研究、生產,或者是解決生產上的問題以便維持產品的 品質,都需要使用生產線上的製程設備來從事生產或實驗工作。

在必須兼顧兩者的情況下,由於目前積體電路製程設備價格昂 貴,每部少則數百萬,動輒上千萬,甚至於上億台幣,設備正常運轉 的時間便成為半導體廠內的稀缺資源。再加上設備隨製程不斷地微縮 化而需持續更新,折舊成本的負擔在在使得設備運轉時間成為生產管 理上最重要的稀缺資源<sup>2</sup>。由於組織必須以特定方式分配、組織時間 以便有效地回應環境需求,此分配、組織時間資源的方式構成了僱員 的工作的時間特性(Fine, 1990: 95)。本文探討的即是晶圓廠為了同 時滿足研究、生產、和維持產品品質的需求,所造就的主要兩類僱員 -技術員與工程師的工作在時間面向上所呈現的特性。

## 貳、文獻探討:組織、工作與時間

生產管理所依據的時間,其特性是客觀、可計算的同質性時間。 為了配合市場、客戶的需求,提供組織內部管理基礎的營運計畫所使 用的日程表(schedule)是以標準的月、週、日、時為單位。而勞動力的 購買亦是如此。這種可計算、可轉換為勞動力價值的商品化的時間概 念,是資本主義生產的重要特徵。這種同質性的時間也成為現代社會 主要的時間概念(Adam, 1995)。為了在每日特定長度的時間內換取 最大的勞動,資本主義生產透過科學管理、勞動分工,以及機器運轉 速度等等來控制工人的工作步調,試圖將工作時間中所存在的「罅隙」 減到最低 (Starkey, 1988: 99-101)。這與過往的手工業或農業,由

<sup>&</sup>lt;sup>2</sup> 根據 2003-2007 年五年間的資料,折舊成本約佔台灣半導體業製造成本的 40%。相較 之下,直接人工佔製造成本的比重僅約 3%(李慧萍,2008)。即便加上員工分紅等 福利項目的支出,台灣半導體製造業的人力成本佔製造成本的比重也低於 10%。

50 政大勞動學報/第二十八期/民國 101年 12月

工作者或者自然界的韻律來決定的生產步調形成了強烈的對比(Hassard, 1989: 17-20)。

然而在工資與勞動時間的交換關係中,即便資方利用計件制 (piece rate)或者科學管理這類精細的管理手段使工人屈從於嚴苛的 時間限制,勞方仍然擁有可操弄的空間(Burawoy, 1979; Hassard, 1989: 20-21)。在這類制度下,工人即使必須一再重覆單調的工序,卻仍 然可以創造以事件為基礎的(event-based)時間經驗。例如 Roy 發現 在機械廠每日單調而冗長的工作時間裡,工人透過發明定時舉行的各 種分享食物、相互捉弄等等遊戲來將每日劃分為幾個區塊。這使得工 人可以稍微忍受似乎無止盡的一日(Roy, 1959)。

因此,不僅在日常生活中人經驗著各種不同性質例如生理的、季 節遞嬗等等的時間,在組織內的時間也是多樣的(Adam, 1995)。這 包括生產管理所依據的同質性、可計算的時間,以及由於不同的工作 特性所產生的各種異質性的時間經驗。學者們採用諸如時間秩序 (temporal order) (Barley, 1988)、時間參照框架 (temporal reference framework) (Zerubavel, 1979; 1981) 、時間結構 (temporal structure) (Orlikowski and Yates, 2002),或者是時間框架(time frame)(Adam, 1995)等內涵相近的詞彙來指稱各種同質性、異質性時間的組合。經 驗研究發現,雖然組織透過時間秩序對於勞方個人或群體置諸時間上 的限制,但後者不只是被動地依從,也能夠取得一定程度的時間自主 性。例如 Fine 透過五個可以用來定性工作之時間特性的因素:週期 (periodicity)、步調(tempo)、時機(timing,指兩活動必須同步) 或者相互調整)、持續時間(duration)和次序(sequence),來探討 工作者如何經驗組織所強加的時間秩序並與之協商(Fine, 1990: 96)。 Fine 研究餐廳廚師,發現他們瞭解並且試圖維持恰當而令自己滿意的 工作步調。在一定的時間壓力下廚師們最能展現自己的能力;過少的 事頭會導致百無聊賴,而過多則易引發不耐、氣憤等等反應(Fine, 1990; 1996) •

從屬於不同時間秩序的僱員之間若需同時進行一項工作,常常可 以發現這類可能引發衝突的情緒反應。這來自於對於事件優先性的認 識不同,由於一方無法及時撥出時間來進行協作,導致某一方被迫處 於等待的不利情況。在實際研究上,可以透過比較兩方時間秩序的構 成來分析其差異程度。例如 Barley 用四個因素來定性時間秩序:事 件或活動發生的次序(sequence)、持續時間(duration)、發生時間 (temporal location) ,以及發生頻率 (rate) (Barley, 1988: 128) , 並透過比較一所社區醫院的放射線科醫事放射師(radiologist)和技 師(technologist)之間時間秩序的差異,來探討兩者的衝突。他的田 野研究發現,由於醫事放射師的工作包括解讀相片、與其它科別醫師 討論檢查結果、對病人家屬解釋病情、主持檢查,以及接聽不定時響 起的來電等等,各項工作的次序不易預測,一項工作持續的時間很短 而且常被不同部門人員打斷。相較之下,技師的主要工作是為病人執 行檢查,每項工作的持續時間較長,工作的重複性較高,而且多半依 照事先排定的時間表進行。由於時間秩序是衡量他人工作的時間架 構,醫事放射師和技師以其各自的工作所呈現的時間秩序去評價對 方:技師發現醫事放射師時常忽略甚至遺忘技師預先排定的工作;醫 事放射師則往往認為技師錯估了事件的重要程度。兩造由於工作的時 間秩序的差異,為了希望對方配合己方的時間秩序,常常引發衝突。 Barley 將醫事放射師和技師的工作時間秩序分別歸類為人類學家 Edward T. Hall 所謂的「多序」(polychronic)和「單序」(monochronic): 前者不注重事件發生的先後次序,偏好同時進行多種活動;而後者則 偏向事先計畫,賦予每一事件完整的處理時段(Barley, 1988: 158)。

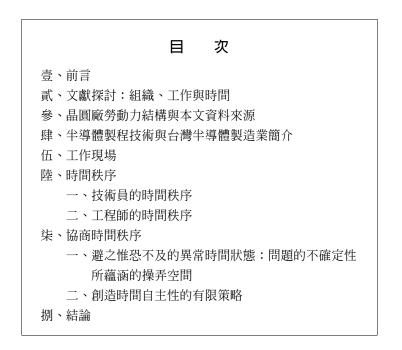

本文借鏡上述的文獻,分析組織所賦予技術員和工程師的時間秩 序,以及他們的因應之道。接下來的第參節,我將交待半導體晶圓廠 的勞動力結構以及本文的資料來源。第肆節簡介半導體製程技術與台 52 政大勞動學報/第二十八期/民國 101年 12月

灣半導體製造業的梗概。第伍節描述工作現場,著重生產線上的時間 安排。第陸、第柒節分別分析技術員與工程師的時間秩序,以及探討 工程師如何協商時間秩序。第捌節則為本文結論。

## 參、晶圓廠勞動力結構與本文資料來源

一個晶圓廠的運作,依產能差異,所需人力約在數百至上千人之 譜。而一個晶圓製造公司的運作除了可能分散各處的晶圓廠外,許多 例如財務、法務、行政等部門則可集中一地。除了這些可集中的部門 之外,各個晶圓廠為維持生產線運作所劃分的部門,其組織架構差異 不大。首先是製造部,主要的組成的人員是生產線上的技術員和管理 生產線的主任(或稱課長)。後者的主要職責爲協調機台產能的調度 和監督技術員的工作。接著是工程部門,依職責不同可分為四類。第 一類是製程研發以及元件工程師,負責製程技術研發和模擬。第二類 是與生產線較密切相關的工程師,包括製程、設備,以及製程整合工 程師,其主要工作是維持穩定的產品品質、提升良率、維護機器設備, 以及改善製程降低生產成本。第三類與生產線上產能的規劃直接間接 相關,包括生產管理、工業工程,和自動化工程師,職責是將生產線 理性化以做最有效率的利用。第四類則包括可靠度、品保、產品及客 服工程師,負責對不良品做缺陷及故障分析,並且構成與客戶溝通的 管道。在上述四類工程師中,第一、四類可集中而非每個廠房所必須, 例如製程技術開發通常集中於某一個廠區進行,研發出成果後再移轉 到各個晶圓廠。第四類工程師也有獨立於生產線的實驗室,其分析測 量的結果可經由電腦網路傳遞至相關人員。第二、三類工程師則是每 個晶圓廠運行必備的人力,與生產線的關係也最密切。

在晶圓廠中,技術員約佔總員工數的一半左右。這些技術員的工 作,是將晶圓(在晶圓廠中稱爲貨)依照指定步驟放入設備機台內(上

貨)進行某項製程,完畢後再將貨取出(下貨,整個過程總稱為 run 貨),以人工方式用推車移往下一道製程的機台旁,或送入自動化傳 輸系統。每個技術員需負責操作數部機台,其數量多寡依據機台特性 如製程時間以及自動化程度而異。例如在某八时晶圓廠中,光微影、 乾蝕刻設備的製程時間較短,每人負責3至4台,而擴散爐管製程時 間較長,每人負責數量則在8部左右(葉文裕、林彥輝,1999:11) <sup>3</sup>。這些技術員的學歷多為高中、職。而工程師依職務不同,學歷自 專科到碩、博士皆有,通常技術研發部門所要求的學歷最高。晶圓廠 在勞動力的組成上最明顯的特徵是性別區隔:生產線上的技術員多由 女性擔任,而工程師則絕大多數為男性<sup>4</sup>。

本文的資料來源是田野記錄以及半結構式的訪談,聚焦於勞動過 程中的時間面向。訪談對象共 14 人,所屬廠家包括各類晶圓廠。其 中包括兩位技術員、1 位製造部主任,以及 11 位工程師(其中女性 工程師佔兩位)。訪談的工程師包括了上述所有第一到第四類工程師, 而以第一、二類為主。14 人中有 2 人曾在同一廠家先後擔任不同職 務、1人曾在不同廠家擔任相同職務,而有兩人曾在不同廠家擔任不 同職務。訪談對象多屬基層員工,訪談進行之時在晶圓廠工作的平均 年資約為4年半。

<sup>,</sup> 晶圓尺寸及製程技術的分類詳第建節。

<sup>&</sup>lt;sup>4</sup> 根據受訪者及方德琳(1997)的說法,台灣的晶圓廠例如台積電早期曾徵聘男性技術員,但在90年代初期之後約十年間幾乎完全消失。這是由於在1992年,台積電將年終分紅與職級掛鉤而引發了男性技術員的怠工,自此資方便開始傾向不聘用男性技術員(方德琳,1997:94)。事實上,晶圓廠對技術員的性別選擇偏好會因情況而改變。例如2002年3月8日兩性工作平等法通過,放寬了女性工作者休假的規定之後,某些晶圓廠便開始募集男性技術員。此外,由於十二吋晶圓的面積、重量皆甚爲可觀,廠商也爲此而在十二吋晶圓廠中使用男性技術員(自由時報,2004/4/24)。晶圓廠的性別區隔現象在各國以不同的方式呈現,例如台積電位於美國的晶圓廠 Wafertech 有爲數不少的男性技術員。

## 肆、半導體製程技術與台灣半導體製造業簡介

除去特殊用途產品外,目前電子資訊業所使用的積體電路晶片泰 半以矽為基材。1947年,貝爾實驗室利用半導體材料鍺發展出第一 個電晶體。其後的 1950年代,電晶體之間仍需以外接導線的方式來 連接。及至 1950年代末期,將多個電子元件與線路整合在同一塊矽 基材上的積體電路(integrated circuit, IC)技術已告成形(Bassett, 2002: Chap 1)。積體電路的發明使得電路的體積能進一步縮小。自積體電 路發明之後,製造的技術已經大致底定,其後數 10年間的進展,相 對於當初的發明而言,是演進的(evolutionary)而非革命性的 (revolutionary)(Plummer et al., 2000: 12)。

製造技術的進展背後的推手是經濟因素,這也是摩爾定律原初的 著眼點:在同一晶片上放入更多的元件有助於降低元件的單位生產成 本(Mollick, 2006:64)。然而在另一方面,由於積體電路製程的步 驟繁多,線路的複雜化會使不良品出現的機會增加,亦即良率降低。 因此,積體電路製造業必須兼顧製程技術的微縮化以及良率的維持。 關於製程的微縮化,業界通常以 DRAM 晶片中的閘極線寬做為度量 製程技術微縮度的指標,這個長度從 1983 年約 1.5 微米(µm,一微 米為百萬分之一米)到 1998 年已縮小到 0.25 微米。及至 2011 年, 此長度更縮小至約 28 奈米(nm,一奈米為十億分之一米)。另一方 面,若以集積度,亦即每個晶片上所包含的電晶體數量來估算,集積 度亦在不斷地增加。集積度在 1 千到 10 萬稱為大型積體電路(LSI), 集積度在 10 萬到 1 千萬則稱為超大型積體電路(VLSI)。以 Intel 所 推出的微處理器為例,1971 年的 4004 包含 2 千 3 百個電晶體,尙屬 於 LSI,至 1982 年的產品 80286 則有 13 萬 4 千個電晶體,已進入 VLSI 的範圍。1998 年推出的 Pentium II 所包含的電晶體數已經達到 750 萬

個(李雅明,1999:229)。而 2006 年推出的 Core 2,包含的電晶體 數量更達數億之譜<sup>5</sup>。

對於目前的積體電路製造業而言,製程的微縮化不僅意味著需要 更先進的生產設備,也常常伴隨著使用更大面積的晶圓(wafer)<sup>6</sup>。 當晶圓的面積增大,每片晶圓可產出的晶片數會增加,亦即產能會增 加。若以每單位面積的晶片成本估算,在扣除設備和材料成本支出的 增加後,增大晶圓的面積有助於降低成本。因此半導體業界所使用的 製程設備,從 1970 年代針對三吋、四吋晶圓設計的設備,經過 1980 年代的五吋、六吋,1990 年代的八吋,目前業界的新購設備,多半 是針對十二吋的晶圓。

至於台灣半導體產業的發展,則是自 1970 年代中期,政府以直 接介入的方式扶植而奠定基礎。當時是從美國 RCA 公司引入積體電 路技術至工研院電子工業發展研究中心(後來改制為電子工業研究 所)。而自 1980 年開始,則以半官方半民間的方式相繼成立了聯華 電子(簡稱聯電,成立於 1980 年)、台灣積體電路(簡稱台積電, 成立於 1987 年)以及世界先進(成立於 1994 年)。自台積電成立後, 民間技術來源和資金籌措相對容易,半導體廠相繼成立,並發展出除 了設備商之外完整的上、中、下游體系。<sup>7</sup>若將利用小尺寸晶圓生產 特殊用途晶片的廠商略去不計,目前台灣的積體電路製造廠,包括了 以晶圓代工,亦即以提供晶片設計公司製造服務為主的台積電、聯電、 世界先進;生產快閃記憶體的旺宏;以及向歐美日韓廠商購買技術專 利,甚至與技術提供者合資設廠,以生產 DRAM (動態隨機存取記 憶體)為主的南亞科、華亞科、茂德、力晶、瑞晶、鉅晶、華邦。近 來年台灣 DRAM 廠因嚴重虧損,許多廠家已轉型、分割為晶圓代工

<sup>&</sup>lt;sup>5</sup> http://www.intel.com/pressroom/kits/quickreffam.htm.

<sup>6</sup> 晶圓是半導體晶圓廠加工的最基本單位,爲圓形薄片。

<sup>1</sup> 目前半導體製程設備絕大多數仍由美、歐、日進口。

廠,甚至出售廠房設備以償債<sup>8</sup>。及至 2011 年,全台在北縣泰山、桃 園林口、竹科、中科,南科五處運作中的矽晶圓廠近四十座(楊瑞臨 2011)。在 2011 年下半年,台灣晶圓代工廠量產的製程技術最小達 28 奈米,與 Intel 微處理器 Core 2 所採用者相當;DRAM 廠則約在 40 奈米,落後於韓國領導廠商。生產 DRAM 這種標準產品的廠家,面 對的是一個在生產過剩與生產不足兩者之間景氣循環波動幅度甚大的 市場。相較之下,晶圓代工業的特性是利用少量多樣化的客戶訂單來 分散風險。就本文所關心的晶圓廠生產線上之實際運作而言,在穩定 產品品質、提升良率來降低成本這一點上,DRAM 與晶圓代工業的 差異並不大。差異較大者有兩點。其一是晶圓代工廠內由於產品線的 複雜化,工程師的勞動強度較高。其二是台灣的 DRAM 廠以購入國 外廠商技術為主,在製程微縮化的研發投入較晶圓代工業者少。

經過數十年的發展,因應日趨複雜的製造過程,積體電路產業已 形成細密的分工形態。目前整個產業的上、中、下游,各負責積體電 路自原料、設備、設計與加工過程的不同階段。其上游包括原料、光 罩、電路設計以及設備供應商。原料包括晶圓片以及加工過程所需使 用的各種化學液、氣體。電路設計則是依照功能需求,以電腦輔助工 具繪製出電路圖。而將電路圖轉寫到玻璃基板上就形成了光罩,光罩 的用途是將電路圖顯影於晶圓上。設備供應商則提供加工晶圓所需要 的各種製程、檢測設備。積體電路產業的中游指的就是一般所稱的晶 圓廠,在此晶圓經過製程設備內各種物理、化學方法的重複施行,最 終在其上形成一個個尙未經過封裝的積體電路晶粒(die)<sup>9</sup>。晶圓廠 中的物理、化學加工法,包括了光微影(photolithography),亦即使 用光罩和光阻劑,利用曝光原理在晶圓上得到所需的圖樣。此外尙有

<sup>8</sup> 台灣半導體產業的歷史發展過程相關文獻可見吳思華、沈榮欽(1999)、張如心、潘 文淵文教基金會(2006)、蔡偉銑(2009)、Hong(1997)、Mathews and Cho(2000)等。

9 依電路設計的差異,一片晶圓可容納數百至上千個晶粒。

氧化(oxidation)、擴散(diffusion)、化學氣相沈積(chemical vapor deposition)、物理氣相沈積(physical vapor deposition)、離子植入 (ion implantation)、乾蝕刻(dry etching)、溼蝕刻(wet etching), 以及化學機械研磨(chemical-mechanical polishing)等等<sup>10</sup>。產業的 下游則包括封裝及測試。封裝是以絕緣材料封合晶粒成為晶片;而測 試則是對完成加工流程的晶片進行電性測試,判斷其是否能達成功能 上的要求。

## 伍、工作現場

晶圓廠在業界一般簡稱為 Fab (fabrication plant 的簡稱)。由於 積體電路元件電路的微細化,空氣中的微塵、人體的皮膚碎屑等等都 會影響產品的良率。為此 Fab 內設有過濾空氣中微粒的裝置,進入前 所有人員都必需經過清潔程序。首先是避免化粧,以防化粧品微粒進 入工廠,再者是必須先穿著無塵衣(bunny suit)、膠鞋,戴手套、 口罩,在空氣洗滌室經壓縮空氣噴去附著於身上的微粒之後才能進入 Fab<sup>11</sup>。

Fab 內的物品基本上可分三類。第一是生產和量測設備,也就是 數百台各式各樣的機台,這些機台上面通常附有顯示機台狀態的螢 幕。生產過程所需使用的消耗品如各種化學液、氣體等則透過位於地 板或天花板內的管線通往機台。第二類是生產的半成品,即完工程度 不同的各種晶圓。這些貨通常以二十四片晶圓為一批(lot),透過塑 膠製的晶舟(boat)承載。技術員上下貨時是以晶舟承載晶圓的方式 進行,上貨之後和下貨之前晶圓在機台上的傳輸則多由設置於機台上

<sup>&</sup>lt;sup>10</sup> 積體電路的製造流程需使用多種有毒氣體及各種酸、鹼液。關於積體電路乃至於一般 電子業對於環境產生的危害,見 Smith, Sonnenfeld, and Pellow (2006)。

<sup>11</sup> 無塵衣的材質爲不透氣纖維,防止衣物及皮膚微粒進入空氣中。

58 政大勞動學報/第二十八期/民國101年12月

的機械手臂代勞。至於貨在晶圓廠內透過人工或自動傳輸設備運送時,則需先將晶舟置入塑膠盒(稱爲晶盒)中<sup>12</sup>。其三類物品則是用以記錄、追蹤貨品流向及機台狀態的電腦。

由於積體電路製程的繁複,不同的產品因設計複雜度的差異,在 Fab 內經過的製程步驟,少則 100 多道,多者 3、400 還未可盡數。 此過程快則 2、30 天,慢則長達 2 個月以上。在這些製程步驟中,基 於其物理、化學原理的不同,大致上被分成黃光(photo,光微影的 簡稱)、擴散(diffusion)、薄膜(thin film)、蝕刻(etching)四 種製程技術部門。而工廠內負責維持生產線的工程師,也依照這四種 技術的分工而被劃分成四個在組織上屬於同一層級的部門,稱為 "module"<sup>13</sup>。在 Fab 內的各種機台,也多半依照製程技術的不同,被 劃分在不同的區域。透過空間上的劃分,不同 module 的工程師便在 各自的區域工作。而技術員也是以四種製程技術的分工來界定,負責 特定 module 的機台。在這種技術分工之下,module 工程師和技術員 雖然分屬不同部門,職責也不同,但卻透過機台而連結在一起。在每 一個 module 內,工程師又依任務的不同,分成負責維修機器的設備 工程師,和負責產品品質及製程參數(程式)的製程工程師<sup>14</sup>。除了 這四個製程技術的 module 之外,另有獨立於這四個 module 之外的製

<sup>&</sup>lt;sup>12</sup> 一個晶盒可裝二十五片晶圓。比一批貨二十四片多出的一片空間可用以放置測試機台用的控片 (control wafer)。一個裝滿二十五片八吋晶圓的晶盒總重約為 5.4 公斤 (葉 文裕、林彦輝,1999:18);十二吋晶圓一盒約重九公斤。

<sup>&</sup>lt;sup>13</sup>有些晶圓廠是區分為五個製程技術部門。從一家由 IBM 離職員工所創設而短暫存在 過的半導體公司 Cogar 的組織圖中可知,這種以製程技術來劃分組織部門的方式在 1970年代初期便已經在美國出現(Bassett, 2002: 316)。

<sup>&</sup>lt;sup>14</sup>每個製程所需的各種條件如溫度、壓力、經過時間、消耗的物質等等都有所差異,這 些不同的組合稱爲製程參數,或稱程式(recipe)。通常一台機器都設定有多種製程 參數,技術員爲產品選擇適當的程式進行製程,而製程工程師則負責微調設定,維持 產品品質的穩定。

程整合部門,對於所有的製程之間的關係有較通盤的瞭解<sup>15</sup>。在晶圓 廠中,每一批貨的生產流程都由電腦上的記錄來掌控。當技術員在執 行某項製程前後,都需在電腦上鍵入資料。透過這些資料不但可以得 知每批貨的動向,也可以用來掌控整個生產線的步調,成為生產管理 的基礎。

由於職責分配的差異,技術員與工程師處身於不同的空間與工時 安排。為了 24 小時不停地運轉的生產線,技術員以四班二輪制執勤。 四班,是指有四個組別,分日班和夜班,每班連續 12 小時,一般早 晚七點或七點半是交班時間; 二輪,指做兩休兩或做三休三,也就 是每一組連續上班兩(三)天,然後休息兩(三)天。在一天 12 小 時的上班時間裡,有兩次各約1小時的用餐休息時間,而同一 module 的技術員在休息時必須輪流以維持生產線的持續運轉。除休息時間 外,技術員幾乎整個上班時間都待在無塵室裡。另一方面,工程師的 上班時間,一般表定為一天九個半小時,從早上八點到下午五點半或 八點半到六點。設備工程師以及部分廠家的製程工程師,則與技術員 一樣需要輪班。工程師的工作空間則包括了辦公區和 Fab。由於工程 師並不負責直接的生產工作,通常是因爲機台、產品的問題,或者需 要做實驗、量測等等才進入 Fab。

Fab 的空間配置並不像一般電子裝配工廠那般,具有一排一排的 組裝線。在積體電路的製造流程中,同一批晶圓可能要經過同一類機 台數次。例如某產品可能要上十數道甚至更多光罩,在上完每道光罩 後又經過許多不同的製程,然後再回到原來的,或同一類機台上第二

<sup>&</sup>lt;sup>15</sup> 在人力方面,一般晶圓廠每個 module 中的技術員約有 10~20 人,製程工程師約 10 ~20 人,設備工程師 20~40 人。製程整合工程師約有 20 人。通常各 module 的工程 師僅熟悉自己 module 的機台及製程,而製程整合工程師則大體上需瞭解所有的製程 在電性上的特性。有些晶圓廠的製程整合部門會有一個次部門,稱為 defect team 的 單位,是利用檢測 (inspection) 機台,以抽樣檢查的方式,監控生產線上產品的品質。

60 政大勞動學報 / 第二十八期 / 民國 101 年 12 月

道光罩。因此,一批貨就在 Fab 內各種機台之間來來回回地穿梭數百次。若以一座月產能3萬片的晶圓廠而言,「任何時刻在線上跑的晶 圓大概有十萬片」(受訪者 A12)。如此多量的晶圓,在數百台機台 間游蕩,再加上每批貨進入生產線的時間不同,進行的製程不一,使 用的是另一種時空劃分的方式來控制。

晶圓廠在最初規畫產能,安置設備之時,工業工程學的計算便不 單純地僅考量物理鄰近性來安排生產線的機台和技術員,而是以貨的 旅程來觀看生產線:

基本上我們當然是讓流程越順越好…你的 route 設計要 讓它很 smooth 地讓它流,但是問題半導體(製程)先天就 是一直回來,所以你就要去看你整個流程要怎麼安排可以讓 它就算回來也不要跳來跳去而能夠最順。所以你要先看看這 個廠要 run 什麼樣的產品什麼樣的製程,然後製程前後之間 的關係是什麼,機台的前後關係是什麼,然後則最大宗的量 去統計出來最 optimized 的 layout 讓它生產出來最有效率。 平均一批貨那時候在工廠跑可能要四 mile,這樣 run, run, run, run, run 要跑四 mile,你人走走四 mile 都很累啊,走四 mile 大概六點多公里,你用走路可能要走兩小時。你可以想想看 那個貨就在 Fab 裡面走了六公里的距離,這還是畫得比較好 的 layout,畫得比較差的 layout 搞不好要跑十公里,那不用 run 貨了每天在 Fab 裡面光跑馬拉松就跑死它了。所以一個 好的 layout 可以把不必要的浪費的距離縮短。 (A10)

透過這種以貨的眼光來觀看生產線的方式,Fab 的空間不只是因 為擺放機台需要佔據物理空間,也轉換成晶圓旅行的距離,並換算成 晶圓旅行所需的時間。這個時間受到各種因素的影響,因此晶圓廠的 生產控制,從技術員上下貨的時間,到機台要如何利用好讓閒置的時

間縮短,乃至於一批一批貨要如何排隊才能最快走完,亦即所謂的派 工(dispatching)問題等等,都成為生產管理的指標。打從晶圓廠建 廠之初,Fab 的空間便已經依照生產效率原則,特別是晶圓的旅行速 度來規畫。

如同其它利用理性化方式來規劃的工廠一般,透過工業工程學的 視角,晶圓廠的運作便可由生產管理的指標來定義。這些指標包括諸 如 cycle time(一片晶圓經過所有製程的時間)、WIP(work in process, 在製品,亦即在生產線上流動的半成品數量)、wph(wafer per hour, 一個機台在單位時間內可以完成的製程量)、uptime & downtime(機 台正常運轉及當機時間)、move(一批貨在機台中完成一道製程, 稱為一個 move)等等<sup>16</sup>。在這些概念化的指標操作之下,Fab 就如同 一個有輸入數據和輸出數據的函數,管理者所在意的是函數的特性, 輸出與輸入之間的關係。而技術員則成為在生產線上必須安置於晶圓 與機台之間的介面。而數百個機台,幾萬片晶圓的持續運動、瞬息萬 變的生產狀況皆及時記錄於電腦中。

台灣晶圓廠生產線資訊化的歷史並不算長。以往在每一批貨上面 都貼有一張"run card",貨每經過一道製程便將完成的時間及負責人 員用筆記錄下來。如果要查一批貨位於何處,只能用人工的方式去查 找。1980 年代末期到 1990 年代初期則開始引進類似超級市場所使用 的紅外線掃瞄系統與電腦整合。此後技術員只要從電腦中查出所負責 的機台現在應該跑什麼貨,根據機台的實際狀況(如目前進行的製程 是否已經執行完成,或者尙需多少時間才能執行完畢),需要上下貨 時只要掃瞄晶盒上的條碼即可。製程若執行完畢,技術員先以目視檢 查晶圓是否顏色異常或者表面有異狀,然後再送至量測機台做量測並

<sup>&</sup>lt;sup>16</sup> 這些指標也是一般製造業常用的指標,例如 cycle time 和 WIP、uptime & downtime 就 是業界通用,但其它的指標因生產性質的差異,可能會有不同的計算方式及名稱。

62 政大勞動學報/第二十八期/民國101年12月

記錄資料,鍵入電腦。完畢後便讓貨跑到下一站。電腦中會顯示某個 特定機台還有多少貨等著 run,它們各別的批號等等,而技術員每天 的工作就是將這些貨一批一批地放到機台裡。在資訊化系統引入後, 每一批貨的情況,技術員所做的每一個動作,都被記錄在電腦內。透 過 Fab 內外電腦之間的網絡,製造部主任可以隨時得知 Fab 內每批貨 的情況。資訊系統並且進一步地整合電腦內的各種資料,將各種生產 管理指標立即地運算出來,可供隨時檢查各個指標的水準。這就是資 訊全景敞視(information panopticon)的效力(Zuboff, 1988: Chap 9): 特定資料可以在事後檢索取得的特性,使得技術員對於貨和對於機台 做的每個動作都無所遁形。而出於管理的需要,技術員無法任意竄改 輸入資料,也沒有觀看特定資料或執行某些動作的權限。

## 陸、時間秩序

#### 一、技術員的時間秩序

如上所述,技術員的工作是將一批批的貨送入機台中進行製程。 生產管理上有什麼方法增加技術員的生產效率呢?製造部主任關心的 是每日的 move 數是否達致標準,以便使晶片能準時出貨,因此會以 發放獎金的制度鼓勵技術員加快生產速度。獎金是以整個班為單位, 規定每月達到一定的 move 數便可取得額外的獎金,也可能採取輪班 的四班之間競爭的方式。雖然如此,由於 move 數大致決定於機台的 產能,超越機台的時間限制並不容易。實際上,move 數的標準「都 是製造部在定的」(A14),也就是說,管理者根據機台產能和貨物 交期等等因素,已經推算出每天應達成的 move 數大約是多少。技術 員的合作趕工,例如去催促上游機台 run 完的貨趕快送過來等等,的 確有可能塡補生產管理系統上的時間孔隙而稍稍增加生產效率。但事

實上,這種獎金制度的功效並不太大,一方面是因為它佔月薪的比例 極低;有些廠家甚至是以主任請客的方式來代替。最重要的,是因為 生產線的步調主要取決於貨和機台的搭配。如果貨很多,機台消化不 完,技術員就會為了上、下貨而奔忙;但有時也會有機台閒置等不到 貨的狀況。在這種情況下生管工程師有效的派工,比督促技術員更能 達到增加生產效率的目的:

我們要那批貨先跑那批貨就會立刻加速,要那批貨後跑 它就立刻減速,我們今天下什麼線明天他們就吃什麼菜,這 個東西影響到Fab線上的狀況影響一個月。我們也可以拿Fab 來做實驗,你今天下錯的東西,一個禮拜後你就可以看到線 上堆貨,你就會看到結果。(A10)

生產管理部門由交期等因素所推算出每日貨品應進行的速度,便 成為技術員一天工作的基礎。就技術員每日的工作而言,工作的順序 (哪批貨要先上)從電腦資料中即可得知,而一項工作(上下貨)的 持續時間短暫。大致決定技術員工作步調的,是貨到達的時間,與機 台空檔時間兩者之間的配合,而這多半並非直接管理者的監督和獎勵 措施便能使其加速。

技術員在表定的上班時間內持續地上下貨,消化在機台前排隊等 待進入機台加工的貨物列。每日上工時,領班會提醒今日工作重點, 例如哪個機台今天是生產瓶頸,應注意將它的閒置時間降到最低。技 術員除了選錯製程或者不愼打破晶圓片之外,對於貨物的品質不負有 責任。因此,上級交付的工作目標是以日為單位,技術員「**只要把每 天的 move 數 run 到就好了**」(A14)。交接下班之後,技術員一天 的工作與責任便告結束。 64 政大勞動學報/第二十八期/民國101年12月

二、工程師的時間秩序

(一)依然受制於生產線的研發工程師:虛構產權的運作

工程師則從屬於不同的時間秩序之下。所有工程部門的經理,都 會在每週固定的時間召開內部會議(稱爲週會),藉以追蹤基層工程 師的工作進度。週會進行的方式,是每個工程師輪流報告當週內的計 畫進度,完成了哪些交付的工作。達成每週的工作目標因而成為工程 師主要的時間限制之一。經理如何訂定每週的進度呢?以研發工程師 爲例:

schedule 當然是上面他們決定的,上面的人說某製程明 年第三季要 ready,那你就可以知道我們機台哪時候要決定, 那機台決定之前一定要有 data 要先出來…所以當上面的人 押 schedule 下來你就自己知道大概什麼時候要做什麼事情。 (A06)

晶圓廠透過預測技術進展,反推回目前應當進行的研發工作,便 成為製程研發工程師的工作時程。晶圓廠的技術研發包括新機台的評 估和新製程的研發兩者。當晶圓廠要購入新機台之前,會先對各設備 商的機台進行評估,視評估結果決定購入何種機台。購入之後再經過 驗機的程序,即由研發部門測試機台的特性,測試完成後機台便移交 製造部。而開發新的製程、新式產品也同樣要經過認證程序,確認製 程技術或產品品質達到一定水準才能進行生產。新製程、新產品的開 發可能在已經交付製造部的機台上進行,因此研發和生產部門必須共 享機台的使用權。晶圓廠先將機台名義上的所有權歸入製造部,再行 分配機台的使用時間。除了製造部之外,任何其他部門要使用生產線 上的機台來從事實驗,都要透過層層的會簽手續向製造部商借機台運 轉時間(稱為「借機」);工程師若欲規避這層手續私下借機,技術

員可予以回絕。這種對於生產工具的虛構產權觀念,在運作上是以保 障生產為目的。

研發工程師的日程表,一方面是配合新機台的購置需求時程,進 行事前的實驗評估工作。另一方面,在利用生產線既有機台開發新製 程上,則受制於生產線的步調:

製造部連 run 他們的貨, run 產品都 run 不出來了,所以 RD 根本沒有時間借機啊<sup>17</sup>。沒有時間借機,也抱怨跟上面的人講,沒有時間借機,當然就做不出結果來啊。(A06)

借機是奠基於機台的虛構產權之運作。還有另一種與之相互搭配 的制度設計,是貨品的虛構產權。兩者相輔相成來保障生產速度不會 受累於研發工作。怎麼做呢?所有為了在市場上交易而生產的貨品, 在生產線上的虛構產權一律歸屬製造部所有,製造部是所有貨的 "owner"。而其它部門為了做實驗而在生產線上跑的晶片,則以從事 該實驗的部門為其"owner"。例如為了開發新製程所使用的實驗晶圓, owner 便是研發部門。這些非歸屬製造部所有的晶圓,一律被嚴加看 管,如同借機手續一般,只有經過重重會簽之後才得以使用機台運轉 的時間。再者,非歸製造部所有的實驗晶圓,除非是所謂的"hot run" <sup>18</sup>,否則對於技術員而言,與一般貨品相較之下並沒有優先性,技術 員不見得要先 run 這些實驗晶圓:

<sup>&</sup>lt;sup>17</sup> 技術研發部門有的廠家簡稱為 TD (Technology Development),有的廠家簡稱為 RD (Research and Development)。本文一律以 RD 代表研發部門。

<sup>&</sup>lt;sup>18</sup> 晶圓廠內基於迫切需要,有"hot run"(或稱 hot lot),或者層級更高的"super hot run (lot)" 可資運用,屬於這個範疇的晶片有優先使用機台時間的權利,當它在生產線上時,有 排除其它 lot 的特權。當它即將利用某個機台時,製造部會讓這個機台保持閒置狀態 等候大駕,讓它儘快通過。這種特殊的範疇屬於配給制,每個部門只能有少數額度供 緊急時使用。一般工程師的責任範圍內很少獲得這種特殊待遇。

你現在研發的可能是明年或後年就要上生產線了…在研 發來講 schedule 是很重要的,但是問題是線上小姐平均…比 方說你每一站都有二十批貨在等,她爲什麼要先 run 你的 貨?就小姐的觀點最簡單嘛,第一個,第一優先當然是 super hot run,然後 hot run 嘛,然後接下來就是產品優先嘛,然 後再來就是 integration(製程整合)lot 優先嘛。所以 RD module 的 lot 其實是 priority 排最低的。 RD module 大概一百個人 裡面我們可以有一批 super hot run、三批 hot run。所以其實 大部分的人帶的貨都是 normal run。 (A06)

對於研發工程師而言,眼下的工作時程是自未來導入新製程的時 間點回溯而成,而以每週為單位呈報實驗成果。表面上看來,研發工 程師不像生產線上那般被各種生產指標精確地訂定每日的工作,而可 自行規畫一週內每天的進度。但在實際上,實驗晶圓被生產管理系統 一視同仁地看待,因此即便研發工程師與生產線的關係較遠,還是在 這種無差別的待遇下被納入生產線的韻律。工程師在表定的上班時間 內常常無法借到機台從事實驗,因此必須等到下班時間過後,其他工 程師已經陸續離去的夜班時間才能如願。

(二) 為問題追逐的生產線工程師: 無法預測的時間秩序

在日班時間內,除了研發工程師之外,還有許多需要競逐機台使 用時間的工程師。這些工程師與生產線的關係更為緊密,包括了製程、 設備,和製程整合工程師。製程和設備工程師是與生產線關係最為密 切的工程師。這兩類工程師同樣必須在每週的週會中報告各種改善製 程、降低生產成本等等的計畫進度。這些計畫與研發工程師開發新製 程的計畫相同,都需要使用機台運轉的時間。然而生產線的持續運行 則將他們納入了更不可預測的時間秩序之中。

為何不可預測呢?因為數以萬計的晶圓在數百部持續運轉的機台 之中流動,設備出差錯,或者各製程之間因種種因素發生意想不到的 交互作用的情況難免會發生,「它本來就是會 low yield (低良率), 機率性來講它就是會偶爾就會,機台不可能永遠都是好的,就像車子 不可能永遠都是好的一樣」(A02);「一個製程從頭到尾要跑好幾 百個步驟,然後你又有那麼多產品,那不出錯的機率實在是太小了啦, 多多少少都會有一些問題」(A01)。事件發生的不可預測性從而成 為工程師時間秩序的一大特徵:

一天常常會因為工廠裡隨時隨地都可能發生任何的事 情,產品可能一下子會出問題,然後 testing 或是不過,或 是有些產品要報廢,或是有些異常,你隨時都要 case by case 的去處理。每天,其實每天工作有點像打仗一樣,每天都會 遇到不同的東西。(A01)

如何知道事件發生,發生後又如何處置呢?在晶圓廠中,貨品品 質的維持是由工程師擔綱。通常在單一機台上都會有數種不同的製程 程式,以因應不同產品或同一產品不同製程順序的製程要求。製程完 成後的結果是否合乎規格(specification,簡稱 spec)是檢測產品品 質的關卡。在每道製程結束之後,除了技術員以目視檢查之外,會經 過檢測機台測度該製程的結果是否合乎標準。技術員將量測結果鍵入 電腦後,若符合規格的產品可繼續製程,不合格的則需由工程師來處 理。這些鍵入電腦內的量測結果,就成為品質控管的資訊。若是製程 結果不合標準,包括貨,及進行該製程的機台的狀態,都成為工程師 必須介入處理的問題。

對於產品製程的品質規格要求分為兩種,一種是與製程穩定度相 關的各種參數,例如若是鍍上一層薄膜,就會有關於該薄膜厚度的容 許誤差範圍,太薄、太厚或是均匀度太差都不合格。另一種則是關於 可容許的污染規格。在製程進行時來自環境及機台內部的各種微粒子 可能造成產品電路短路、斷路等後果,因此對於微粒的數目和大小範 圍也有一定的限制。當一道製程結束後,技術員將量測結果鍵入電腦 時,各個製程的規格資料就會自動把關。當產品參數不符規格時,電 腦就會將貨扣留(hold),不允許其繼續接下來的製程。這時技術員 就會通知製程工程師來處理。如何通知呢?技術員通常會先用電話撥 打工程師的分機。如果工程師因開會或位在 Fab 裡它處而未接電話, 技術員便會用 Fab 內外都能聽見的電話廣播系統呼叫工程師。

受呼叫的工程師到達現場後,需判斷問題貨物如何處理。有些製 程允許重做一次,或者多做一些額外的製程如清洗晶圓等等補救之後 放行(稱為「解掉」,或稱「解 hold」);工程師也可能基於經驗直 接放行。資訊監控的機制就透過對於產品的責任劃分將工程師納入了 生產線。雖然資訊系統的設計讓工程師對於貨品有較技術員高的控制 權,只有工程師有權力「解 hold」,然而正因如此使得工程師受到生 產的壓力,必須儘快將異常的貨作妥善的處理。每一次技術員輸入量 測資訊的時候,便可能是貨物異常狀態的開始,若真有異常,工程師 便得進入 Fab 修補其異常狀態。從這個角度看來,技術員每天 run 貨 的過程裡,其實都在持續不斷地透過電腦宣告貨的狀態。當貨被宣告 為正常時,技術員和工程師兩者相安無事,但是當貨被 hold 住,也 就是宣告為異常時,工程師就會被技術員告知處理異常貨物的義務。 異常的貨經過工程師的種種補救措佈處理後,形態可說是各色各樣, 但只要符合規格,脫離異常狀態即可。因此,沒有標準的正常,只有 相對於死貨(指無法事後補救完成後續製程,只有報廢一途的晶圓) 這種異常狀態的正常。如果將貨物的狀態放進 Fab 的空間脈絡來看, 貨的異常狀態意味著工程師進 Fab 工作一定量的時間。因此,貨對於 工程師而言其實是被負面定義的,只有在異常時刻才屬於工程師。

上述所談的是負責產品製程穩定度的製程工程師。但製程由機台

進行,製程出問題往往也導因於機台不穩定,此時技術員也會馬上通 知設備工程師。就如同異常的貨會被電腦 hold 住一樣,當機台當機 無法正常運轉時,技術員也會在電腦上宣告機台的不正常狀態,稱為 "wait",當機台進入 wait 狀態時,電腦上機台的當機時間 (downtime) 指標就開始起跳,downtime 越多代表機台的妥善率越差,設備工程 師的責任也就越重。因此,異常的貨品/機台如果不做立即的處理, 或者問題無法立刻解決的話,透過虛構產權的作用,這些異常的貨品 /機台就會被歸到各工程部的名下,各種追蹤異常的時間指標也就開 始起跳,成為每週的週會中被主管關心的問題。

#### (三) 技術員與工程師的時間秩序比較

從上文中我們可以瞭解技術員和工程師的時間秩序如何構成。首 先,晶圓廠在研究發展上,預估導入新製程的時機,然後從該時點往 後推算研發工程師目前應該從事的實驗,並以调會的方式追蹤進度。 而在生產方面,則以交貨期限回推,扣除數個月的生產流程所需時間, 然後推估出技術員每日所必須進行的 move 數量。以生產速度、機台 使用最大化為尙的時間資源分配並未將生產與研發過程中的不確定性 完全納入考量,而是以虛構產權的設計來追蹤工程師的成果。對於與 生產線關係最密切的製程與設備工程師而言,技術員是正常/異常時 間的媒介者,也是虛構產權轉移的執行者。技術員每日的工作順序較 為固定,決定於機台閒置時間與貨品到達時間的相互配合。而生產線 工程師則除了每週固定的計畫進度之外,尙需排除生產線上的突發事 件。這些事件不只發生時間不定,依據嚴重程度的差異,其持續的時 間,也就是解決所需的時間也長短不一。而技術員與工程師之間的關 係,則在發生問題需要協作時表露無疑。一般協作時通常是被認定為 較具專業、知識的一方在時間上佔有優勢,另一方為了配合必須等待。 例如在 Barley 所研究的醫院放射科,技師必須等待醫事放射師的空

70 政大勞動學報/第二十八期/民國101年12月

檔。但即便技師找到了醫事放射師也不見得能保證能佔用後者的時間,因為在放射師的判斷之下,技師的檢查未必在那個時點具有優先性(Barley, 1988: 145)。然而在晶圓廠內卻是技術員在協作時佔優勢。在虛構產權轉移的運作下,工程師必須立即著手處理突發事件。

但工程師所面對的事件不只發生時間無法預測,定義和解決也充 滿了不確定性。事件的定義,也就是事件要成其為事件(關係到事件 發生的頻率),以及事件已經解決而不再成為事件(從成為事件到事 件的解決,即為事件的持續時間)上的不確定性,也使得工程師在時 間秩序上有了操弄的空間。

## 柒、協商時間秩序

# 一、避之惟恐不及的異常時間狀態:問題的不確定性所蘊涵 的操弄空間

讓我們先以 module 內部的例子來說明。如上文所述,當貨品發 生異常時,製程工程師需做補救措施,而設備工程師需要確認機台的 狀況。然而確認機台是否有問題也並不是一件可以立刻判明的事。例 如判斷貨品的異常,通常是基於測量數據不符規格,由此推斷機台發 生異常。但設備工程師可以質疑對機台不利的量測結果,認為並非機 台的運作有問題,而是由於量測機台或者量測過程出了問題。此時製 程工程師就必須提出種種證據,找出到底是哪裡出了差錯。而這個過 程也成為兩方工程師衝突的來源。如果已經確定是機台發生異常,那 麼設備工程師便需停機維修。為了減少當機的時間,設備工程師常常 在維修過程中,尙未確認機台已經完全恢復穩定水準之前,便開始讓 機台 run 貨。而這麼一來往往會生產出異常的產品,增加製程工程師 的工作負擔,因此後者常需嚴加把關,確認機台的穩定度。但機台是 否恢復穩定,正如同機台是否出差錯的問題一樣,都不是立即分明的 事。因此,機台的運轉,常常是兩方妥協的結果。事件的解決和事件 的定義都蘊涵著不確定性。

以上是在單一 module 內發生的情況。如果牽涉的問題並非單一 module,就進入了下面的過程:

因為半導體的製程是連續的,你 photo 出問題,你 wafer 如果今天出問題的話,說實在的如果在那個站沒有發現到的 話,你可能已經 run 到 thin film 去了。但是 photo 之後可能 會經過 diffusion, diffusion 完後可能到 thin film,到 thin film 或是到 etching 檢測的時候才發現這批貨有問題,那那個時 候怎麼辦?大家查原因,查到最後的時候就是大家推來推 去, 啊那是 photo 問題啊, 那是 thin film 問題啊, 那是 diffusion 問題啊, 然後大家推來推去。 (A11)

半導體廠內以技術劃分的四個 module (黃光、擴散、薄膜、蝕 刻),其中包括各自的製程和設備工程師。如同前文所述,在每一道 製程完成後,會有基本的參數測量成為品管的第一道關卡。然而由於 製程的複雜性以及之間的相互作用,品管的第一道關卡未必能發現潛 在的問題。在第一道關卡之後經過數道製程,又會有檢測機台抽檢經 過這些製程的貨品,查驗微粒子的污染等等參數,此為品管的第二道 關卡。負責這個檢測機台的是製程整合部門。當製程整合工程師經檢 測結果發現貨有異常時,便需釐清責任歸屬。

誰都不願意先承認自己有問題,因爲這牽涉到異常時間狀態的指標,也代表即將伴隨而來的大量繁瑣工作。那麼如何判定問題出在哪裡呢?製程整合工程師利用的也是電腦資料庫中貨品的資訊:

解決問題的方式,通常就是根據線上的一些run 貨的 data 記錄值,去看一些共通性,因爲你通常出問題的話絕對不太 72 政大勞動學報 / 第二十八期 / 民國 101 年 12 月

可能是單一 case,一定會有一些連串性,從 run 貨機台的共 通性或是一些量測出來的數據,異常值你可以去判斷可能是 哪個地方出問題。…可是有時候根本不需要做就可以判別它 的問題,也許是一連好幾個 lot,做一些共通性一看就知道 是你這個機台經過的,那你這個機台當時也許都有異常的記 錄,那你當然想都不用想就是你的!對不對? (A01)

就是你的!也就是「你家」的。工程師們常常會問道,這是哪一 家的貨?而技術員也會使用家這個字,例如「把貨送到下一家」等等。 「家」用來指涉由技術劃分所界定的部門,在生產線上,四個 module 都各自成家,製程整合部也成一家,技術員依照所屬機台性質也像工 程師一樣分成4家。至於研發部門,也如同生產線上一般依技術而區 分為4或5家,並且也有專門負責確認各家責任的整合部門。「家」 這個字的使用常常在界定責任時出現,例如上引文所提的情況,就是 製程整合工程師在確認問題到底出在哪一家時。此字在漢文化中的意 義,不僅涉及父系繼承原則裡的系譜、財產關係,也指稱生活功能團 體。而在 Fab 的脈絡裡所出現的「家」,則與日常生活脈絡中會說「那 是你家的事」來劃分事物與人我的關係類似,是利用親屬關係的隱喻, 來討論其他經濟、社會、政治及儀式等種種關係的慣用語(idiom) (Wolf, 1982: 90)。從使用脈絡來看,「家」是技術分工下各部門人 員在界定彼此責任時,用於指稱其它部門的方便稱呼,而在言談中使

用「家」,用意往往是在區分「你家」跟「我家」。也就是說,在分 工之下,工程師與技術員時常在區分人我的責任,因而僅管「家」是 個隱喻,但卻也表示了半導體廠內在界定彼此責任的爭議相當頻繁<sup>19</sup>。

<sup>&</sup>lt;sup>19</sup>在工作場合中,以「家」這個字來區辨人我並非以平行的製程技術分工為特徵的晶圓 廠所獨有。例如在百貨公司裡的專櫃人員,也會使用「家」來區辨某品牌產品是否為 自己所代理販售。

時常發生的爭議是製程整合部欲確認各家的責任,使不同的 module 之間產生相互卸責的對抗。而各 module 內部也會因為對問題 的起因與解決方式有不同的看法,而發生製程與設備工程師間的對 抗,如同上文所述。工程師與技術員之間也因關心不同而發生衝突。 除了對抗之外,部門之間及部門內部也會合作,例如對設備工程師與 技術員來說,將機台修好對兩造都有利,因此除了界定彼此責任之外, 也會互助;兩 module 之間也可能為了解決問題而合作。晶圓廠中由 於產品品質的責任歸屬問題,每天搬演著這些分分合合的過程。簡單 的問題可以在短時間就確認責任歸屬,例如利用儀器分析近期數個製 程完畢之後才出現的微粒子的化學成份,追查使用該化學物質進行製 程的機台,便可及早判斷是哪家的機台需要檢查維修。然而複雜問題 的發生常常涉及許多部門,從而使得責任的邊界不斷地游移。問題的 發現和解決也往往經過很長的時間,例如貨品可能經過前面所提的兩 道品管關卡都正常,但到了製造流程已經全部結束後的電性、可靠度 種種測試才發現問題,這時距離問題的發生點可能已是一、兩個月後, 責任劃分又更加困難,而牽連的部門也就更廣。

然而問題的界定為何迭有爭議,使得當事者在事件發展之初有否 認自家責任的可能性呢?受訪者 A01 在前面的引文所談到的,只是相 對簡單的情況。對於生產線工程師而言,事件的發生可能由自己 module 的技術員、或者其他 module 的工程師,或是由製程整合工程師等等 告知。在第一道關卡便檢查出來的問題,通常也較容易處理。在技術 員通知後,製程工程師和設備工程師若能確認問題,那麼接下來的工 作便比較明確。但如果是牽涉到兩個部門以上的問題,確認問題本身 便不是一件容易完成的工作。正如前文所述,製程與設備工程師尙且 可以爭論單一量測儀器的量測結果,那麼經過多道製程之後的量測結 果更不在話下。量測結果的記錄是解決問題的基礎,然而量測儀器本 身也可能是問題的來源。因此,在晶圓廠中,不只製程的品質、機台 74 政大勞動學報/第二十八期/民國 101 年 12 月

的穩定度是透過量測儀器來監控。由於負責測量的儀器也有穩定度的 問題,它們也需要由其它的儀器、機台、晶圓所生產出的資訊來監控。 晶圓、機台、量測儀器和電腦相互之間構築成了一個綿密的網絡,工 程師就透過這個物與物相互關連的網絡中所產生的數據來下判斷。

只要是機台生產出來的資訊,便有可商榷的餘地,這是責任的界 定為何會有許多爭議空間的原因。因此,工程師在面對問題時,首先

「要先判斷說這些 data 是不是可以信任」(A08)。初步的工作便是 判斷量測結果是否合理、判斷量測機台是否準確。在這個過程中,重 複量測、用不同種類的晶圓來測試量測機台,或者檢視量測機台近期 的表現,都是衡量它穩定度的手法。如果發現問題是真的存在,那麼 下一步的工作才是找出問題所在處。其難處在於問題的產生常是交互 作用的結果,在某個機台發現問題產生,不見得那個機台就是問題的 根源,因此必須設計實驗來確認問題。一位工程師舉例說明了解決問 題的手法:

比如說今天是在產品上看到那種 defect<sup>20</sup>,然後你要解 決它,可是你要解決一個問題,你必須要知道一個問題是怎 麼出來的,可是問題是,通常在生產線上不是說在這邊看到 問題,表示問題就出在這一站,因爲有時候其實你看的東西, 你在檢查的時候是中間已經隔了很多站,所以你不知道是那 一站出來的,所以你就要慢慢 trace back,然後有時候你 trace back 不一定發生問題那一站你看得到,所以你就要設計一 些實驗説你要怎麼樣才能看到,然後你是不是真的要在產品 上試,如果你能在空片(指純粹做實驗用的晶圓)上面重複 這樣的實驗而發現同樣的 defect,那這樣你不就可以用空片 來做,而不要用產品嗎?所以就是有幾個工作你要同時去

<sup>&</sup>lt;sup>20</sup> Defect 指缺陷,包括微粒子等使晶片不能正常運作的因素。

做,你先是可能產品去走同樣的製程,然後你去看說是不是 發生同樣的問題,如果今天那個問題還是只出現在產品,那 這是不是跟它的 pattern (指產品依設計不同,各層之間堆疊 的方式不同)有關係,還是說今天是在黃光或蝕刻部門的時 候出現這個問題,還有就是你看不看得到這些 defect,它是 不是可能跟你是產品或是空片有關,可是這也跟今天你的這 個薄膜容易看或不容易看有關,所以你要想一些辦法說你要 怎麼樣去判斷它到底是什麼樣的情況。 (A08)

就上例而言,基於成本考量最好以空片來經過那些有問題的製程,以測試那些被懷疑為有問題的機台群,然後慢慢將追蹤範圍縮小, 最後鎖定某個機台。若此機台在生產線上有數台屬於同一型,就可以 利用之前都經過同樣製程的晶圓,到這個機台時分成兩批,一批在懷 疑有問題的機台上跑,另一批則用另一台相同型號的機台來跑,如果 出來的結果是前者有問題,後者沒有,那麼大致上便可確定問題所在。 這種比較的手段不僅是各類工程師解決問題的基礎,也是研發新製程 時使用的方法。

雖然問題的界定可能有爭議,但如果責任大致底定,那麼要著手 解決問題仍然受限於自己與他人的時間秩序。我們可以就上例的工程 師所言,來探討在解決問題過程中工程師受到哪些時間限制。首先, 要判斷資料是不是可信,除了分析電腦記錄的歷史資料之外,也可能 需要多次使用量測機台。而量測機台與生產機台一樣,在晶圓廠內的 數量也是有限的。若各部門工程師和技術員同時都要使用某一量測機 台,則需按先來後到依序;工程師在使用上並沒有優先權。確認量測 結果是工程師舉證責任的第一步。在此步驟之後,若已經確認問題所 在,那麼有問題的貨品就透過虛構產品的運作,劃歸爲工程部門所有, 而成爲每週週會的檢討對象。而工程師爲了解決問題,在透過設計實 76 政大勞動學報/第二十八期/民國101年12月

驗從事持續時間不等的實驗來比較數據這個過程中,又被納入了生產 線的律動之中,需將自己的工作時間配合生產線以伺機取得機台運轉 時間。

#### 二、創造時間自主性的有限策略

而工程師在這種事件發生的時點、頻率不固定,解決問題所需時 間長短不一且受制於機台閒置時間的有無,並且每週固定被檢討進度 的時間秩序之下,有何創造時間自主性的可能呢?在此舉出工程師幾 個對於此時間秩序的小規模應對方式。

首先便是前文所述及的,利用確認問題的困難這一點。否認問題 可以獲得些許緩衝時間,也可能就此免去花費時間在一個責任不在自 身的問題上。其二是延緩虛構產權的生效時間點。例如在機台當機時, 由於修理機台往往並非短時間內可以完成的工作,因此對於任何可能 的時間縫隙,設備工程師都習慣性地想要爭取。最好是能夠在修理機 台時,還讓機台在電腦上表現為正常狀態,偷取虛擬空間(電腦上的 downtime 指標)和實際發生事件(機台當機,理應算 downtime)之 間的時間差,這種態度使設備工程師常常與技術員產生對立:

跟設備(工程師)比較常會有不高興啦。因爲有時候, 因爲我們線上就是 run 貨嘛,然後機台會有它的狀態,如果 說機台當機的話,設備都很不希望我們機台掛 wait,就是待 他們來維修嘛,反正設備都不希望我們掛 wait,然後常常就 會因爲掛機台狀態什麼的這些方面跟設備有一些衝突。(A14)

之所以產生對立是因為在 wait 狀態,機台的責任在於設備工程 師,但如果技術員私底下接受工程師的要求,不將機台設於 wait 狀 態,就會造成實際上機台當機,但電腦上所顯示的機台卻處於正常狀 態的情形。如果被製造部主管發現機台在電腦上顯示為正常,應進行

生產活動卻未進行,導致生產指標無法反映實際情況,技術員當然就 會受到關切。雖然技術員的工作是由製造部監督,不需聽命於工程師, 且於協作時在時間上佔有優勢,但由於工程師修機讓機台回復正常運 轉也有助於技術員進行製程,因此技術員也偶會順應要求,讓機台的 妥善率指標下降的程度稍微減低。

此外,工程師可以藉由平均分配每週的工作成果,來面對上級每 週固定時段的成果驗收:

他們每次開會都要有些進展,每次都要有些 progress, 但是老實說做研發也不會都有 progress,哪有每個禮拜定時 就有新發現。一開始進來,因爲你之前沒有一個 data base, 所以你每次上去報的時候都是 fresh data,剛出來的 data, 然後就要被拿上去報。那現在就是比較好,現在就是說有一 些存糧,每個人都會有存糧。今天報的其實是,等於是之前 的,新的 data 就是下一次再報,這樣子就感覺沒有那麼大 的壓力。 (A06)

這與計件工時的制度下,工人保留一部分的趕工成果不上繳,以 備接下來數日萬一無法趕工之需的情況類似(Burawoy, 1979: 58)。 這種調節工作成果,取有餘而補不足的方式,可以說是工程師以成果 存量爲標準創造了自己的時間表。這個時間表一方面可以應對上級的 固定時間表,與之維持一定的時間差,另一方面也提供了緩衝,減低 實驗過程的不確定性所帶來的時間壓力。

## 捌、結論

綜而言之,由於積體電路製程的複雜性和生產線上機台數量及種 類的多樣性,生產線上工程師的工作有下列特徵。第一是不斷發生, 而且無法預測何時出現的事件。透過量測機台的監控,工程師不斷地 被提醒問題的發生,繼而去定義問題,並解決問題。在這個過程中, 首先問題要成其爲問題,有賴於各部門對於問題界定有沒有共識。而 共識能不能形成,則取決於工程師的實驗結果是否能夠說服所有參與 者。第二個特徵則是對於複雜問題的解決,方法是實驗比較,而由於 積體電路製程耗時,再加上實驗必須取得機台運轉時間,此過程往往 十分冗長。

如果我們以 Barley 所應用的時間秩序上的「多序」和「單序」 來區分晶圓廠的工作時間秩序,可以發現技術員的工作是較為單序 的,而工程師工作的特性則是多序。技術員直接面對生產線上的機台 和產品,依照機台進行製程的時間,安排讓貨不斷地流動;而工程師 則要應付隨時突發的各種事件。然而晶圓廠生產線較 Barley 所研究 的放射科複雜得多。在後者,醫事放射師是透過醫生、技師的告知, 或者接聽電話等等人際互動來得知並完成一項工作。而在前者,工程 師雖然也是透過技術員或是其他工程師而得知事件的發生,但事件的 發生有一個重要的基礎,亦即資訊的全景敞視。透過電腦資料庫中各 種機台和製程的品質規格的把關,工程師面對著不定時出現的問題, 這是迫使工程師必須在多序的時間秩序下工作的基礎。

在 Barley 的研究中,對於醫院放射科而言,由於醫事放射師的 專業能力被認定為較技師重要,醫事放射師除了要主持檢查以外還要 面對醫生、病人家屬等等以提供判斷,因而技師必須配合醫事放射師 的時間秩序。然而正是由於醫事放射師成為他人必須諮詢的對象,才 造成了多序的工作時間秩序。晶圓廠中的工程師也是如此。工程師由 於被賦予解決問題的責任,因而納入了多序的工作時間秩序之中。然 而,這種時間秩序並不因為其專業能力較技術員來得受重視,便可以 讓他人來適應自己的時間秩序。反而是透過虛構的機台產權的作用, 工程師必須等到機台恰巧輪空才能進行實驗,而這無法預測的時間空

隊更增加了工程師工作的多序性。此外,機台輪空亦往往發生在晚間 下班時間過後,生產線的步調因為工程師陸續下班相對和緩之時。因 此,工程師常常不得不延長工作時數來獲得解決問題所需的機台時 間。而以技術員而言,雖然技術員一人必須負責數台機台,但由於每 批貨上下貨的時間點不一,加上進行每項製程需要一定量的時間,因 此較能夠掌握作業的次序,相對上而言屬於單序的時間秩序。到了每 天表定的下班時間,技術員的工作就告完全結束,只需交接給下一班 人員即可。然而對於工程師而言,表定的下班時間只代表著當日的多 序形態因相關人員離開,可能暫時獲得緩和。在多序的時間秩序下, 不僅事件的發生對於工程師而言是無法預測的,而且問題往往不能在 發生的當下馬上解決,而需透過持續期間不等的實驗才能獲得解答。

在生產、研究,以及維持產品品質皆需使用機台的情況下,晶圓 廠以製造部佔有機台使用時間的措施來保障生產。而在確保品質方 面,則以隸屬平行層級的工程部門之間的責任劃分為特徵。透過技術 員/工程師的責任區分,所有關於品質的問題皆委由工程師處理,並 透過虛構產權的運作和轉移來監控工程師,形成了兩者單序/多序的 時間秩序:技術員的工作次序較能預測,持續時間較短,而工程師的 工作難以預測,持續時間長短不一。相較於技術員,工程師雖在專業 能力上較受重視,但由於機台虛構產權的作用,工程師與技術員之間 的互動,依據的往往不是透過專業上的差異而想像的主從關係。

上文提及工程師在協商時間秩序時採用的幾個策略。而技術員又 是如何呢?就技術員而言,資訊化的工作現場並不必然代表體力耗費 不高。在自動化程度較小的晶圓廠裡,因為各家製程機台以及各種量 測儀器的分佈,技術員做量測,或者將貨移到特定機台處時,需要在 廠內四處移動。而在自動化程度較高的晶圓廠裡,即便在自己負責的 區域內工作也需要在上下貨時來回於電腦、量測儀器、各種機台與自 動化傳輸系統之間。根據研究統計,在某八时晶圓 DRAM 廠,技術 員每小時平均要走 1,300 步 (葉文裕、林彥輝,1999:25)。若以步 距 50 公分計,則在每天約 10 小時的工作時間裡,技術員需走上 6、 7 公里。如前所述,由於製稈順序固定,每個製稈又需一定量的時間, 技術員的工作形態屬於較為單序的,亦即事件依序發生。然而技術員 並不見得要隨著事件的發生即刻做相應的處理,例如機台完成某個製 程便立即去下貨、並上下一批貨。若是以這種方式進行,由於兩相鄰 事件之間時間間隔較短,技術員的體力負荷會增加。由於電腦上可以 看到所負責的機台還有哪些貨等著 run,生產管理單位隨時都可以從 電腦裡得知這些資訊瞭解生產線的狀況,並監督技術員的工作。但是 技術員也利用這些資訊來調整自己工作的節奏,將貨與機台做最好的 時間搭配,使電腦裡該生產指標保持在一定水準。亦即,技術員能夠 考慮貨、機台、電腦記錄的資料這三者之間的關係,並將身體的移動 頻率放入此關係中一併考慮,以減少體力的付出。因此,技術員雖然 因為機台不斷完成製程,必須在製程完成後一定時間內上貨,且需尋 找下一批應該進機台的貨目前所在位置(追貨),同時也等於被貨追 著跑,但仍然能夠透過調合貨、機台、電腦記錄資料之間的關係,將 事頭用較省時、省力的方式完成,在生產線忙碌之際爭取到片刻的時 間罅隙。

工程師亦可採取和技術員類似的方式,例如匯整同時發生的多個 事件,預先估算各事件的處理時間、重要程度等等,甚至事先規劃動 線以便減少步行距離,然後在進入 Fab 之後按照事先想定計畫完成。 然而與技術員相對單序的工作時間秩序相較,生產線上的工程師所遭 遇的是不定期發生的問題事件,往往一個問題尚未解決完畢另一個問 題又接著發生。由於在工程師著手處理之際可能又會發生其它非預期 事件,打亂原有步調,因此這種爲因應問題發生之多序特性的事先規 畫有時而窮。在工作進行中,受到機台運轉時間取得不易的干擾,使 得不可預測性增加,工程師往往必須延長工作時間。再加上從事實驗

常常歷經一段不算短的時間,因此工程師不但每日的工作是呈現多序 的形態,這種形態也因為實驗的同時進行而擴展到數日、週或甚至月。 這使得工程師應付多序工作的形態,不只是以每日為單位。而對工程 師定期追蹤、驗收成果,既是由於多序工作下需要確保各項工作持續 進行,更進一步保證了這種時間秩序不會輕易因每日的結束便告緩 和。

因此,相較於技術員而言工作的順序明確,上下貨持續時間短暫, 工程師面對多序的時間秩序,受到技術員和其它工程師的監控,往往 迷航於紛至沓來的問題而無法正確判斷著手的優先次序。這牽涉到工 程師能夠自主判斷的裁量權,與組織內上下層級之間的關係有關,本 文未能觸及。本文透過時間秩序的角度探討晶圓廠的勞動過程,期能 提供其與上述問題及薪資制度、內部勞動力市場之間關係的研究基 礎,以爲半導體產業,甚至前半段製程與晶圓廠類似的面板產業之勞 動過程研究的參考。

## 參考文獻

一、中文部分

方德琳,1997,《專業科技僱員的勞動體制研究》,臺灣大學社 會學研究所碩士論文。

自由時報,2004,〈科技業擴大徵才 技術員搶手〉,4月24日。 吳思華、沈榮欽,1999,〈台灣積體電路產業的形成與發展〉,

見蔡敦浩編,《管理資本在台灣:台灣產業發展的邏輯》,

頁 57-150,台北:遠流。

- 李雅明,1999,《半導體的故事》,台北:新新聞。

- 李慧萍,2008,〈匯率變動對 IC 產業的影響〉,經濟部技術處 產業技術知識服務計畫(IT IS)(http://www.itis.org.tw)。

- 張如心、潘文淵文教基金會,2006,《矽說台灣:台灣半導體產 業傳奇》。台北:天下文化。

- 張維安、高承恕,1996,〈政府與企業-台灣半導體產業發展的 分析〉。東亞經濟管理與彈性生產國際學術研討會,清華大

- 學社會人類學研究所,10月3-6日,新竹。

- 葉文裕、林彥輝,1999,《半導體作業設備與人體計測尺寸評估》, 台北:行政院勞工委員會勞工安全衛生研究所。

- 楊瑞臨編,2011,《2011 半導體年鑑》,新竹:工研院產經中 心。

- 蔡偉銑,2009,〈技術官僚與產業升級:台灣 1970 年代 IC 計畫 的重新檢視〉,《人文及社會科學集刊》,21(1):25-99。

二、英文部分

Adam, Barbara, 1995, *Timewatch: The Social Analysis of Time*. Cambridge: Polity Press.

- Barley, Stephen R., 1988, On Technology, Time, and Social Order: Technically Induced Change in the Temporal Organization of Radiological Work. Pp. 123-169. in *Making Time: Ethnographies* of High-Technology Organizations, edited by Frank A. Dubinskas. Philadelphia: Temple University Press.

- Bassett, Ross Knox, 2002, To the Digital Age: Research Labs, Startup Companies, and the Rise of MOS Technology. Baltimore: Johns Hopkins University Press.

- Burawoy, Michael, 1979, Manufacturing Consent: Changes in the Labor Process under Monopoly Capitalism. Chicago: University of Chicago Press.

- Ceruzzi, Paul E., 2005, Moore's Law and Technological Determinism: Reflections on the History of Computing. *Technology and Culture* 46(3): 584-593.

- Fine, Gary Alan, 1990, Organizational Time: Temporal Demands and the Experience of Work in Restaurant Kitchens. Social Forces 69(1): 95-114.

- ——, 1996, *Kitchens: The Culture of Restaurant Work*. Berkeley: University of California Press.

- Hassard, John, 1989, Time and Industrial Sociology. Pp. 13-34. in *Time, Work and Organization*, edited by Paul Blyton, John Hassard, Stephen Hill, and Ken Starkey. London: Routledge

- Hong, Sung Gul, 1997, The Political Economy of Industrial Policy in East Asia: The Semiconductor Industry in Taiwan and South Korea. Northampton, MA: Edward Elgar.

- Mathews, John A. and Dong-Sung Cho, 2000, *Tiger Technology: The Creation of a Semiconductor Industry in East Asia.* Cambridge: Cambridge University Press.

- Miller, Peter and Ted O'Leary, 2007, Mediating Instruments and Making Markets: Capital Budgeting, Science and the Economy. *Accounting, Organizations and Society* 32: 701-734.

- Mollick, Ethan, 2006, Establishing Moore's Law. *IEEE Annals of the History of Computing* 28(3): 62-75.

- Orlikowski, Wanda J. and JoAnne Yates, 2002, It's about Time: Temporal Structuring in Organizations. *Organization Science* 13(6): 684-700.

- Plummer, James D., Michael D. Deal, and Peter B. Griffin, 2000, Silicon VLSI Technology: Fundamentals, Practice, and Modelling. Upper Saddle River, NJ: Prentice Hall.

- Roy, Donald F., 1959, "Banana Time": Job Satisfaction and Information Interaction. *Human Organization* 18(4): 158-168.

- Smith, Ted, David A. Sonnefeld, and David Naquib Pellow, eds. 2006, Challenging the Chip: Labor Rights and Environmental Justice in the Global Electronics Industry. Philadelphia: Temple University Press.

- Starkey, Ken, 1988, Time and Work Organisation: A Theoretical and Empirical Analysis. Pp. 95-117. in *The Rhythms of Society*, edited by Michael Young and Tom Schuller. London: Routledge.

- Wolf, Eric R., 1982, *Europe and the People without History*. Berkeley: University of California Press.

- Zerubavel, Eviatar, 1979, *Patterns of Time in Hospital Life*. Chicago: Chicago University Press.

- ------ (1981). Hidden Rhythms: Schedules and Calendars in Social Life. Chicago: Chicago University Press.

- Zuboff, Shoshana, 1988, *In the Age of the Smart Machine*. New York: Basic Books.

## The Investigation of the Temporal Order of the Labor Process in Semiconductor Fabs

Tzung-De Lin\*

### Abstract

Contemporary semiconductor manufacturing is characterized by the erasure of the boundary between research and production, the arrangement that seeks to accommodate to the intricacy of chip making process and the rapidity of technology change. The rapidity of technology change in semiconductor manufacturing, frequently couched in terms of the so-called 'Moore's Law,' maintains at a speed that the number of transistors that can be put on an integrated circuit doubles every one to two years. The indistinguishability between laboratory and factory, however, makes the allocation of the machine time—both for research and for production purposes—a prominent factor that shapes the temporal order of work in semiconductor fabs.

This paper analyzes the temporal order of technicians' as well as engineers' work. Technicians are exempted from handling problems that arise in the production process, and their work is characterized by short, successive tasks in a predictable sequence—a 'monochronic' order. In contrast, due to the complexity of semiconductor manufacturing, engineers face

#### 86 政大勞動學報/第二十八期/民國101年12月

problems that arise randomly, and are forced to undertake several tasks which last for various lengths of time simultaneously—their work is in a 'polychronic' order. With the machine time monopolized by the production department, difficulty in gaining access to the machine time for experimentation, the basis for both problem-solving and research work, contributes further to the polychronicity of engineers' work. In semiconductor fabs, miniaturization trend dictates the way machine time is allocated, which in turn leads to the long working hours of engineers.

**Keywords:** Semiconductor Industry, Semiconductor Fabs, Labor Process, Temporal Order